Streaming SIMD Extensions

Este artigo não cita fontes confiáveis. (Setembro de 2021) |

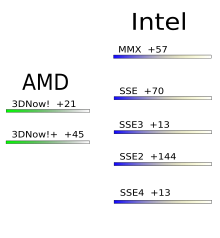

SSE (Streaming SIMD Extensions, inicialmente chamado ISSE, de Internet Streaming SIMD Extensions) é um conjunto de instruções do tipo SIMD projetado pela Intel. O nome completo significa "Extensões SIMD para streaming". O SSE traz 70 novas instruções em relação ao conjunto de instruções anterior, do Pentium MMX.

O SSE foi primeiro conhecido como KNI, de Katmai New Instructions, onde Katmai era o apelido do primeiro Pentium III com núcleo revisto. Durante o projeto Katmai a Intel procurava distingui-lo da sua linha anterior de produtos, particularmente do projeto Pentium II.

O SSE foi uma resposta à tecnologia 3DNow! da AMD, lançada um ano antes. Mas a AMD rapidamente contra-atacou, aproveitando do projeto da Intel e adicionou suporte às instruções SSE, começando assim a era do famoso processador Athlon XP.

A Intel ficou desapontada com o MMX, sua primeira iniciativa de desenvolvimento SIMD para IA-32. O MMX tinha dois grandes problemas: ele reusava registradores de ponto flutuante, o que fazia com que a CPU ficasse impossibilitada de trabalhar simultaneamente com instruções de ponto flutuante e SIMD. Por isso, o paralelismo só era conseguido com instruções de aritmética com inteiros.

O SSE adiciona oito novos registradores 128-bits, conhecidos como XMM0 até XMM7. Cada registro pode armazenar quatro números 32-bit de ponto flutuante ao mesmo tempo (single-precision). As extensões de 64 bits, tanto na Intel quanto da AMD, acrescentam mais 8 registros XMM8 até XMM15. Além deles foi também adicionado um novo registrador, de controle e de status, chamado MXCSR.

Como esses novos registradores de 128 bits são estados de programa adicionais que o sistema operacional (SO) deve preservar entre mudanças de contexto de tarefas, eles devem permanecer desabilitados até que o sistema operacional os habilite explicitamente. Isto significa que o SO deve saber como usar as instruções FXSAVE e FXRSTR, que são o par de instruções estendidas que podem, respectivamente, salvar e restaurar todos os estados dos registradores x87 e SSE, de uma única vez. Este suporte foi rapidamente estendido para todos os principais sistemas operacionais para IA-32.

Como o SSE inclui suporte a ponto flutuante, ele tem mais usos do que o MMX, pois atualmemente as placas de vídeo podem tratar internamente todos os cálculos com inteiros. As operações SIMD inteiras ainda podem ser realizadas com 8 registradores de 64 bits do MMX. Como se sabe, os registradores MMX são obtidos renomeando-se (ou aliasing) os 8 registradores da FPU. Posteriormente, no SSE2, a Intel complementou o SSE com suporte a cálculos inteiros. Apesar de redundantes, as operações MMX podem ser executadas com as operações SSE, o que oferece maior desempenho em situações limitadas.

O primeiro CPU a ter suporte ao SSE foi o Pentium III, que compartilhava recursos entre o SSE e o FPU. As aplicações eram compiladas de forma a utilizar instruções FPU e SSE em paralelo, mas os processadores Pentium III não eram capazes de operar estes dois tipos de instruções simultaneamente (num mesmo ciclo). Estas limitações reduziram a eficiência do chamado pipelining, embora os registros isolados XMM permitiam instruções SIMD e operações escalares de ponto flutuante serem misturadas mas não tão eficientes quanto o modo MMX/floating point.

Versões posteriores

editar- SSE2 foi introduzida com os processadores Pentium 4, e trouxeram melhorias significativas ao SSE (que alguns programadores passaram a chamar de "SSE1"). SSE2 adds new math instructions for double-precision (64-bit) floating point and 8/16/32-bit integer data types, all operating on the same 128-bit XMM vector register-file previously introduced with SSE. SSE2 enables the programmer to perform SIMD math of virtually any type (from 8-bit integer to 64-bit float) entirely with the XMM vector-register file, without the need to touch the (legacy) MMX/FPU registers. Many programmers consider SSE2 to be "everything SSE should have been", as SSE2 offers an orthogonal set of instructions for dealing with common datatypes.

- SSE3 chamado de Prescott New Instructions, é um upgrade incremental ao SSE2, adicionando instruções matemáticas orientadas à DSP (DSP-oriented) e algumas instruções de manipulação de processos (thread).

- SSSE3 é um upgrade ao SSE3, adicionando 16 novos códigos (opcode).

- SSE4 é uma melhoria do padrão antecessor e adiciona um ponto de instrução do produto, diversas instruções adicionais (do tipo integer), uma instrução do tipo popcnt, entre outras.